| Age | Commit message (Collapse) | Author | Lines |

|---|

|

|

|

|

|

Update mdbook to 0.4.42

This updates mdbook to 0.4.42

Changelog: https://github.com/rust-lang/mdBook/blob/master/CHANGELOG.md#mdbook-0441

There were some significant changes that I would like to get early testing on.

This also updates rust-by-example which was required due to an update to the theme file.

|

|

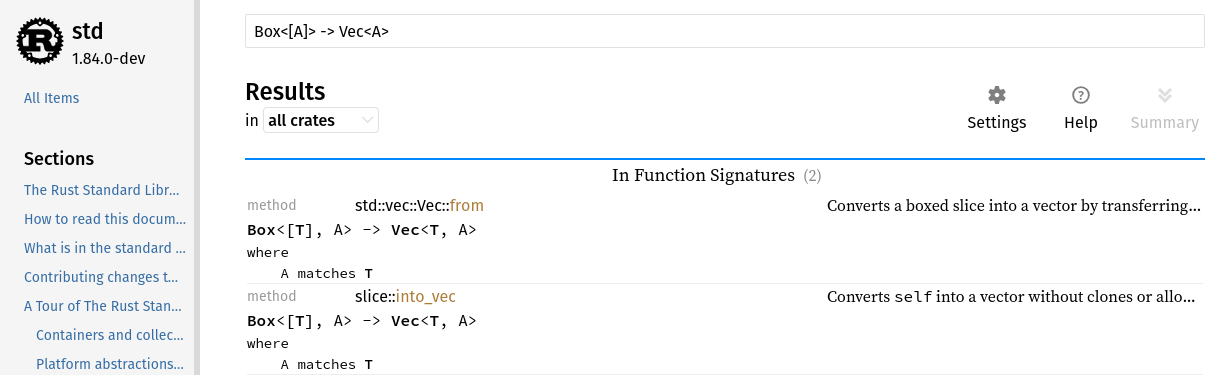

rustdoc-search: simplify rules for generics and type params

**Heads up!**: This PR is a follow-up that depends on #124544. It adds 12dc24f46007f82b93ed85614347a42d47580afa, a change to the filtering behavior, and 9900ea48b566656fb12b5fcbd0a1b20aaa96e5ca, a minor ranking tweak.

Part of https://github.com/rust-lang/rust-project-goals/issues/112

This PR overturns https://github.com/rust-lang/rust/pull/109802

## Preview

* no results: [`Box<[A]> -> Vec<B>`](http://notriddle.com/rustdoc-html-demo-12/search-sem-3/std/index.html?search=Box%3C%5BA%5D%3E%20-%3E%20Vec%3CB%3E)

* results: [`Box<[A]> -> Vec<A>`](http://notriddle.com/rustdoc-html-demo-12/search-sem-3/std/index.html?search=Box%3C%5BA%5D%3E%20-%3E%20Vec%3CA%3E)

* [`T -> U`](http://notriddle.com/rustdoc-html-demo-12/search-sem-3/std/index.html?search=T%20-%3E%20U)

* [`Cx -> TyCtxt`](http://notriddle.com/rustdoc-html-demo-12/search-sem-3-compiler/rustdoc/index.html?search=Cx%20-%3E%20TyCtxt)

## Description

This commit is a response to feedback on the displayed type signatures results, by making generics act stricter.

- Order within generics is significant. This means `Vec<Allocator>` now matches only with a true vector of allocators, instead of matching the second type param. It also makes unboxing within generics stricter, so `Result<A, B>` only matches if `B` is in the error type and `A` is in the success type. The top level of the function search is unaffected.

- Generics are only "unboxed" if a type is explicitly opted into it. References and tuples are hardcoded to allow unboxing, and Box, Rc, Arc, Option, Result, and Future are opted in with an unstable attribute. Search result unboxing is the process that allows you to search for `i32 -> str` and get back a function with the type signature `&Future<i32> -> Box<str>`.

- Instead of ranking by set overlap, it ranks by the number of items in the type signature. This makes it easier to find single type signatures like transmute.

## Find the discussion on

* <https://rust-lang.zulipchat.com/#narrow/stream/393423-t-rustdoc.2Fmeetings/topic/meeting.202024-07-08/near/449965149>

* <https://github.com/rust-lang/rust/pull/124544#issuecomment-2204272265>

* <https://rust-lang.zulipchat.com/#narrow/channel/266220-t-rustdoc/topic/deciding.20on.20semantics.20of.20generics.20in.20rustdoc.20search>

|

|

|

|

|

|

Update grammar in wasm-c-abi's compiler flag documentation

This PR adjusts the grammar of the `wasm-c-abi` compiler flag documentation. See the inline comments within the PR for details.

|

|

Stabilize s390x inline assembly

This stabilizes inline assembly for s390x (SystemZ).

Corresponding reference PR: https://github.com/rust-lang/reference/pull/1643

---

From the requirements of stabilization mentioned in https://github.com/rust-lang/rust/issues/93335

> Each architecture needs to be reviewed before stabilization:

> - It must have clobber_abi.

Done in https://github.com/rust-lang/rust/pull/130630.

> - It must be possible to clobber every register that is normally clobbered by a function call.

Done in the PR that added support for clobber_abi.

> - Generally review that the exposed register classes make sense.

The followings can be used as input/output:

- `reg` (`r[0-10]`, `r[12-14]`): General-purpose register

- `reg_addr` (`r[1-10]`, `r[12-14]`): General-purpose register except `r0` which is evaluated as zero in an address context

This class is needed because `r0`, which may be allocated when using the `reg` class, cannot be used as a register in certain contexts. This is identical to the `a` constraint in LLVM and GCC. See https://github.com/rust-lang/rust/pull/119431 for details.

- `freg` (`f[0-15]`): Floating-point register

The followings are clobber-only:

- `vreg` (`v[0-31]`): Vector register

Technically `vreg` should be able to accept `#[repr(simd)]` types as input/output if the unstable `vector` target feature added is enabled, but `core::arch` has no s390x vector type and both `#[repr(simd)]` and `core::simd` are unstable. Everything related is unstable, so the fact that this is currently a clobber-only should not be considered a stabilization blocker. (https://github.com/rust-lang/rust/issues/130869 tracks unstable stuff here)

- `areg` (`a[2-15]`): Access register

All of the above register classes except `reg_addr` are needed for `clobber_abi`.

The followings cannot be used as operands for inline asm (see also [getReservedRegs](https://github.com/llvm/llvm-project/blob/llvmorg-19.1.0/llvm/lib/Target/SystemZ/SystemZRegisterInfo.cpp#L258-L282) and [SystemZELFRegisters](https://github.com/llvm/llvm-project/blob/llvmorg-19.1.0/llvm/lib/Target/SystemZ/SystemZRegisterInfo.h#L107-L128) in LLVM):

- `r11`: frame pointer

- `r15`: stack pointer

- `a0`, `a1`: Reserved for system use

- `c[0-15]` (control register) Reserved by the kernel

Although not listed in the above requirements, `preserves_flags` is implemented in https://github.com/rust-lang/rust/pull/111331.

---

cc ``@uweigand``

r? ``@Amanieu``

``@rustbot`` label +O-SystemZ +A-inline-assembly

|

|

Co-authored-by: Jubilee <workingjubilee@gmail.com>

|

|

|

|

|

|

|

|

Co-authored-by: SparrowLii <liyuan179@huawei.com>

Co-authored-by: Jieyou Xu <jieyouxu@outlook.com>

|

|

functions instead

|

|

`{ignore,needs}-{rustc,std}-debug-assertions` (#2101)

|

|

|

|

|

|

|

|

Rollup of 5 pull requests

Successful merges:

- #131261 (Stabilize `UnsafeCell::from_mut`)

- #131405 (bootstrap/codegen_ssa: ship llvm-strip and use it for -Cstrip)

- #132077 (Add a new `wide-arithmetic` feature for WebAssembly)

- #132562 (Remove the `wasm32-wasi` target from rustc)

- #132660 (Remove unused errs.rs file)

Failed merges:

- #131721 (Add new unstable feature `const_eq_ignore_ascii_case`)

r? `@ghost`

`@rustbot` modify labels: rollup

|

|

Remove the `wasm32-wasi` target from rustc

This commit is the final step in the journey of renaming the historical `wasm32-wasi` target in the Rust compiler to `wasm32-wasip1`. Various steps in this journey so far have been:

* 2023-04-03: rust-lang/compiler-team#607 - initial proposal for this rename

* 2024-11-27: rust-lang/compiler-team#695 - amended schedule/procedure for rename

* 2024-01-29: rust-lang/rust#120468 - initial introduction of `wasm32-wasip1`

* 2024-06-18: rust-lang/rust#126662 - warn on usage of `wasm32-wasi`

* 2024-11-08: this PR - remove the `wasm32-wasi` target

The full transition schedule is in [this comment][comment] and is summarized with:

* 2024-05-02: Rust 1.78 released with `wasm32-wasip1` target

* 2024-09-05: Rust 1.81 released warning on usage of `wasm32-wasi`

* 2025-01-09: Rust 1.84 to be released without the `wasm32-wasi` target

This means that support on stable for the replacement target of `wasm32-wasip1` has currently been available for 6 months. Users have already seen warnings on stable for 2 months about usage of `wasm32-wasi` and stable users have another 2 months of warnings before the target is removed from stable.

This commit is intended to be the final step in this transition so the source tree should no longer mention `wasm32-wasi` except in historical reference to the older name of the `wasm32-wasip1` target.

[comment]: https://github.com/rust-lang/rust/pull/120468#issuecomment-1977878747

|

|

rustc_codegen_llvm: Add a new 'pc' option to branch-protection

Add a new 'pc' option to -Z branch-protection for aarch64 that enables the use of PC as a diversifier in PAC branch protection code.

When the pauth-lr target feature is enabled in combination with -Z branch-protection=pac-ret,pc, the new 9.5-a instructions (pacibsppc, retaasppc, etc) will be generated.

|

|

|

|

we encountered this in https://github.com/rust-lang/rust/pull/131038

kinda felt like an unspoken rule so here's a more concrete

clarification.

|

|

Rollup of 11 pull requests

Successful merges:

- #131153 (Improve duplicate derive Copy/Clone diagnostics)

- #132025 (fix suggestion for diagnostic error E0027)

- #132303 (More tests for non-exhaustive C-like enums in FFI)

- #132492 (remove support for extern-block const intrinsics)

- #132587 (Revert "Avoid nested replacement ranges" from #129346.)

- #132596 ([rustdoc] Fix `--show-coverage` when JSON output format is used)

- #132598 (Clippy: Move some attribute lints to be early pass (post expansion))

- #132601 (Update books)

- #132606 (Improve example of `impl Pattern for &[char]`)

- #132608 (document `type_implements_trait`)

- #132609 (docs: fix grammar in doc comment at unix/process.rs)

r? `@ghost`

`@rustbot` modify labels: rollup

|

|

Support clobber_abi and vector registers (clobber-only) in PowerPC inline assembly

This supports `clobber_abi` which is one of the requirements of stabilization mentioned in #93335.

This basically does a similar thing I did in https://github.com/rust-lang/rust/pull/130630 to implement `clobber_abi` for s390x, but for powerpc/powerpc64/powerpc64le.

- This also supports vector registers (as `vreg`) as clobber-only, which need to support clobbering of them to implement `clobber_abi`.

- `vreg` should be able to accept `#[repr(simd)]` types as input/output if the unstable `altivec` target feature is enabled, but `core::arch::{powerpc,powerpc64}` vector types, `#[repr(simd)]`, and `core::simd` are all unstable, so the fact that this is currently a clobber-only should not be considered a blocker of clobber_abi implementation or stabilization. So I have not implemented it in this PR.

- See https://github.com/rust-lang/rust/pull/131551 (which is based on this PR) for a PR to implement this.

- (I'm not sticking to whether that PR should be a separate PR or part of this PR, so I can merge that PR into this PR if needed.)

Refs:

- PPC32 SysV: Section "Function Calling Sequence" in [System V Application Binary Interface PowerPC Processor Supplement](https://refspecs.linuxfoundation.org/elf/elfspec_ppc.pdf)

- PPC64 ELFv1: Section 3.2 "Function Calling Sequence" in [64-bit PowerPC ELF Application Binary Interface Supplement](https://refspecs.linuxfoundation.org/ELF/ppc64/PPC-elf64abi.html#FUNC-CALL)

- PPC64 ELFv2: Section 2.2 "Function Calling Sequence" in [64-Bit ELF V2 ABI Specification](https://openpowerfoundation.org/specifications/64bitelfabi/)

- AIX: [Register usage and conventions](https://www.ibm.com/docs/en/aix/7.3?topic=overview-register-usage-conventions), [Special registers in the PowerPC®](https://www.ibm.com/docs/en/aix/7.3?topic=overview-special-registers-in-powerpc), [AIX vector programming](https://www.ibm.com/docs/en/aix/7.3?topic=concepts-aix-vector-programming)

- Register definition in LLVM: https://github.com/llvm/llvm-project/blob/llvmorg-19.1.0/llvm/lib/Target/PowerPC/PPCRegisterInfo.td#L189

If I understand the above four ABI documentations correctly, except for the PPC32 SysV's VR (Vector Registers) and 32-bit AIX (currently not supported by rustc)'s r13, there does not appear to be important differences in terms of implementing `clobber_abi`:

- The above four ABIs are consistent about FPR (0-13: volatile, 14-31: nonvolatile), CR (0-1,5-7: volatile, 2-4: nonvolatile), XER (volatile), and CTR (volatile).

- As for GPR, only the registers we are treating as reserved are slightly different

- r0, r3-r12 are volatile

- r1(sp, reserved), r14-31 are nonvolatile

- r2(reserved) is TOC pointer in PPC64 ELF/AIX, system-reserved register in PPC32 SysV (AFAIK used as thread pointer in Linux/BSDs)

- r13(reserved for non-32-bit-AIX) is thread pointer in PPC64 ELF, small data area pointer register in PPC32 SysV, "reserved under 64-bit environment; not restored across system calls[^r13]" in AIX)

- As for FPSCR, volatile in PPC64 ELFv1/AIX, some fields are volatile only in certain situations (rest are volatile) in PPC32 SysV/PPC64 ELFv2.

- As for VR (Vector Registers), it is not mentioned in PPC32 SysV, v0-v19 are volatile in both in PPC64 ELF/AIX, v20-v31 are nonvolatile in PPC64 ELF, reserved or nonvolatile depending on the ABI ([vec-extabi vs vec-default in LLVM](https://reviews.llvm.org/D89684), we are [using vec-extabi](https://github.com/rust-lang/rust/pull/131341#discussion_r1797693299)) in AIX:

> When the default Vector enabled mode is used, these registers are reserved and must not be used.

> In the extended ABI vector enabled mode, these registers are nonvolatile and their values are preserved across function calls

I left [FIXME comment about PPC32 SysV](https://github.com/rust-lang/rust/pull/131341#discussion_r1790496095) and added ABI check for AIX.

- As for VRSAVE, it is not mentioned in PPC32 SysV, nonvolatile in PPC64 ELFv1, reserved in PPC64 ELFv2/AIX

- As for VSCR, it is not mentioned in PPC32 SysV/PPC64 ELFv1, some fields are volatile only in certain situations (rest are volatile) in PPC64 ELFv2, volatile in AIX

We are currently treating r1-r2, r13 (non-32-bit-AIX), r29-r31, LR, CTR, and VRSAVE as reserved.

We are currently not processing anything about FPSCR and VSCR, but I feel those are things that should be processed by `preserves_flags` rather than `clobber_abi` if we need to do something about them. (However, PPCRegisterInfo.td in LLVM does not seem to define anything about them.)

Replaces #111335 and #124279

cc `@ecnelises` `@bzEq` `@lu-zero`

r? `@Amanieu`

`@rustbot` label +O-PowerPC +A-inline-assembly

[^r13]: callee-saved, according to [LLVM](https://github.com/llvm/llvm-project/blob/6a6af0246bd2d68291582e9aefc0543e5c6102fe/llvm/lib/Target/PowerPC/PPCCallingConv.td#L322) and [GCC](https://github.com/gcc-mirror/gcc/blob/a9173a50e7e346a218323916e4d3add8552529ae/gcc/config/rs6000/rs6000.h#L859).

|

|

|

|

|

|

|

|

The original issue has been fixed, the workaround is no longer necessary.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

This commit is the final step in the journey of renaming the historical

`wasm32-wasi` target in the Rust compiler to `wasm32-wasip1`. Various

steps in this journey so far have been:

* 2023-04-03: rust-lang/compiler-team#607 - initial proposal for this rename

* 2024-11-27: rust-lang/compiler-team#695 - amended schedule/procedure for rename

* 2024-01-29: rust-lang/rust#120468 - initial introduction of `wasm32-wasip1`

* 2024-06-18: rust-lang/rust#126662 - warn on usage of `wasm32-wasi`

* 2024-11-08: this PR - remove the `wasm32-wasi` target

The full transition schedule is in [this comment][comment] and is

summarized with:

* 2024-05-02: Rust 1.78 released with `wasm32-wasip1` target

* 2024-09-05: Rust 1.81 released warning on usage of `wasm32-wasi`

* 2025-01-09: Rust 1.84 to be released without the `wasm32-wasi` target

This means that support on stable for the replacement target of

`wasm32-wasip1` has currently been available for 6 months. Users have

already seen warnings on stable for 2 months about usage of

`wasm32-wasi` and stable users have another 2 months of warnings before

the target is removed from stable.

This commit is intended to be the final step in this transition so the

source tree should no longer mention `wasm32-wasi` except in historical

reference to the older name of the `wasm32-wasip1` target.

[comment]: https://github.com/rust-lang/rust/pull/120468#issuecomment-1977878747

|

|

|

|

Co-authored-by: Jieyou Xu <jieyouxu@outlook.com>

|

|

|

|

People often parse `-vV` output to get to the host triple, which is

annoying to do. It's easier to just get it directly.

|

|

This changes the naming to the new naming, used by `--print

target-tuple`.

It does not change all locations, but many.

|

|

|

|

|

|

assembly

|

|

|

|

|

|

joshtriplett:style-guide-binop-heuristic-assignment-only, r=calebcartwright

style-guide: Only use the new binop heuristic for assignments

This avoids pathological cases where chains of binops get progressively

deeper.

|

|

Remove support for `-Zprofile` (gcov-style coverage instrumentation)

Tracking issue: #42524

MCP: https://github.com/rust-lang/compiler-team/issues/798

---

This PR removes the unstable `-Zprofile` flag, which enables ”gcov-style” coverage instrumentation, along with its associated `-Zprofile-emit` configuration flag.

(The profile flag predates and is almost entirely separate from the stable `-Cinstrument-coverage` flag.)

Notably, the `-Zprofile` flag:

- Is largely untested in-tree, having only one run-make test that does not check whether its output is correct or useful.

- Has no known maintainer.

- Has seen no push towards stabilization.

- Has at least one severe regression reported in 2022 that apparently remains unaddressed.

- #100125

- Is confusingly named, since it appears to be more about coverage than performance profiling, and has nothing to do with PGO.

- Is fundamentally limited by relying on counters auto-inserted by LLVM, with no knowledge of Rust beyond debuginfo.

|

|

|

|

|